# A Dynamically Recompiling ARM Emulator

3<sup>rd</sup> year project report 2000-2001 University of Warwick

> Written by David Sharp

Supervised by Graham Martin

#### Abstract

Dynamically recompiling from one machine code to another can be used to emulate modern microprocessors at realistic speeds. This report is a discussion of the techniques used in implementing a dynamically recompiling emulator of an ARM processor for use in an emulation of a complete computer system.

#### Keywords

Emulation, Dynamic Recompilation, Binary Translation, Just-In-Time compilation, Virtual Machine, Microprocessor Simulation, Intermediate Code, ARM.

## Contents

| 1. Int         | roduction                             | 7  |

|----------------|---------------------------------------|----|

| 1.1.           | What is emulation?                    | 7  |

| 1.2.           | Applications of emulation             | 7  |

|                | Processor emulation techniques        | 9  |

| 1.4.           | -                                     | 13 |

| 2. An          | alysis                                | 16 |

| 2.1.           |                                       | 16 |

| 2.2.           | Identifying the problem               | 18 |

|                | Getting started                       | 20 |

| 2.4.           | The System Design                     | 21 |

| 3. <b>Dis</b>  | sassembler                            | 23 |

| 3.1.           | Purpose                               | 23 |

| 3.2.           | ARM decoding                          | 23 |

| 3.3.           | Design                                | 24 |

| 4. Int         | erpreter                              | 26 |

| 4.1.           | 1                                     | 26 |

|                | The problem with JIT                  | 26 |

| 4.3.           | The HotSpot <sup>TM</sup> alternative | 26 |

| 4.4.           | Quantifying the JIT problem           | 27 |

| 4.5.           | Faster decoding                       | 28 |

| 4.6.           | Interfaces                            | 29 |

| 4.7.           | The emulation loop                    | 30 |

| 4.8.           | Implementation                        | 31 |

| 4.9.           | Debugging                             | 32 |

| 4.10.          | Compatibility                         | 33 |

| 5. <b>Re</b>   | compilation                           | 35 |

| 5.1.           |                                       | 35 |

| 5.2.           | Methods of generating native code     | 35 |

| 5.3.           | The use of intermediate code          | 36 |

| 6. Ar          | mlets – An Intermediate Code          | 38 |

| 6.1.           | Purpose                               | 38 |

| 6.2.           | The 'explicit-implicit problem'       | 38 |

| 6.3.           | Options                               | 39 |

| 6.4.           | Characteristics of Armlets            | 40 |

| 6.5.           | The Program Counter                   | 42 |

| 7. <b>Pr</b> o | ofiler                                | 43 |

| 7.1.           | Purpose                               | 43 |

| 7.2.           | Characteristics of a chunk            | 43 |

| 7.3.           | 6                                     | 45 |

| 7.4.           | Testing                               | 47 |

| 7.5.           | Unrecompilable code                   | 48 |

| 8. <b>Cod</b>                         | e Optimisation                                        | 53 |  |  |  |

|---------------------------------------|-------------------------------------------------------|----|--|--|--|

| 8.1.                                  | The optimiser                                         | 53 |  |  |  |

| 8.2.                                  | The nature of the source code                         | 53 |  |  |  |

| 8.3.                                  | The requirements of optimisation                      | 54 |  |  |  |

| 8.4.                                  | Traditional compiler optimisations                    | 54 |  |  |  |

| 8.5.                                  | Java run-time optimisation techniques                 | 56 |  |  |  |

| 8.6.                                  | Conditional Blocks                                    | 56 |  |  |  |

| 8.7.                                  | Redundant condition flag calculation elimination      | 58 |  |  |  |

| 9. Nat                                | ive Code Generator                                    | 60 |  |  |  |

| 9.1.                                  | Overview                                              | 60 |  |  |  |

| 9.2.                                  | Instruction selection                                 | 60 |  |  |  |

| 9.3.                                  | Register allocation options                           | 62 |  |  |  |

| 9.4.                                  | Dynamic register allocation                           | 63 |  |  |  |

| 9.5.                                  | Condition flag calculations                           | 64 |  |  |  |

| 9.6.                                  | Control Flow                                          | 66 |  |  |  |

| 9.7.                                  | Constants                                             | 67 |  |  |  |

| 9.8.                                  | Emitting machine code                                 | 69 |  |  |  |

| 9.9.                                  | Invoking native code                                  | 70 |  |  |  |

| 9.10.                                 | Debugging                                             | 70 |  |  |  |

| 10. C                                 | onclusion                                             | 71 |  |  |  |

|                                       | Evaluation                                            | 71 |  |  |  |

|                                       | Future extensions                                     | 75 |  |  |  |

| 10.3.                                 | Skills learned                                        | 75 |  |  |  |

| 10.4.                                 | Final conclusions                                     | 76 |  |  |  |

| Referenc                              | es                                                    | 77 |  |  |  |

| Bibliography                          |                                                       |    |  |  |  |

| Acknowl                               | edgements                                             | 88 |  |  |  |

| Appendix A – Overview of ARM assembly |                                                       |    |  |  |  |

| Appendix B – Armlet definition        |                                                       |    |  |  |  |

| Appendix                              | Appendix C – Example code generation 9                |    |  |  |  |

| Appendix                              | x D – Source code                                     | 98 |  |  |  |

| Appendix                              | x E – Glossary of Terms                               | 99 |  |  |  |

| Appendix                              | Appendix F – Advice on attempting similar projects102 |    |  |  |  |

## Index of Figures

| Figure 1- Screenshot of the emulator of the Manchester Baby, originally built in 1948      | 8  |

|--------------------------------------------------------------------------------------------|----|

| Figure 2 - The Fetch-Decode-Execute loop of a processor or interpreting emulator           | 10 |

| Figure 3 - The dynamic recompilation decision process                                      | 11 |

| Figure 4- The execution of threaded code                                                   | 12 |

| Figure 5 - ARM's semiconductor partners who manufacture processors                         | 16 |

| Figure 6 - The Nintendo Gameboy Advance, one of many portable ARM-based devices.           | 17 |

| Figure 7 - R15 in 26-bit-PC ARM processors, containing both the PC and PSR                 | 19 |

| Figure 8 - System Object Model                                                             | 22 |

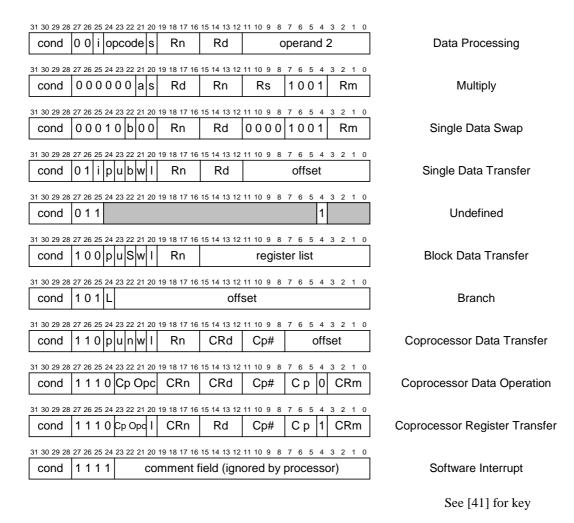

| Figure 9 - ARM instruction set encoding                                                    | 23 |

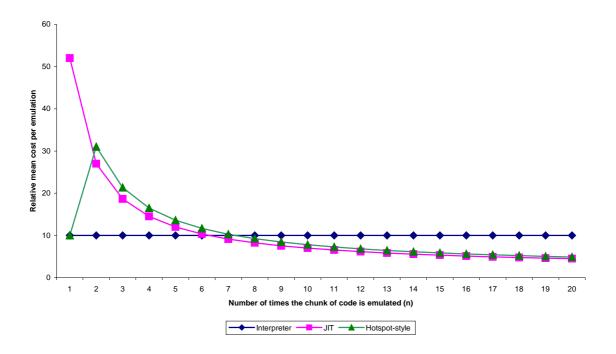

| Figure 10 - The relative average cost per emulation of different emulation methods         | 27 |

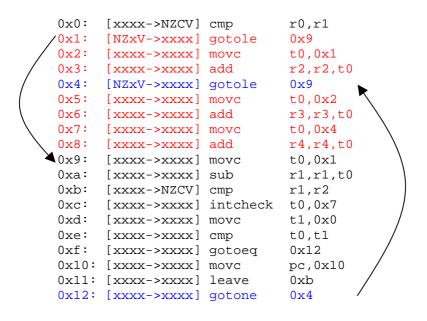

| Figure 11 - The format of the interpreter's instruction decode table for ADD instructions  | 28 |

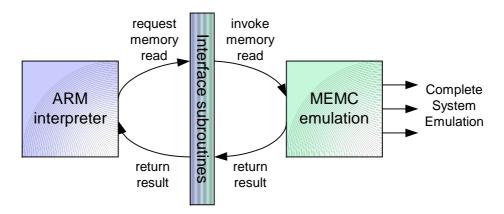

| Figure 12 - Example of the interface used to separate ARM and MEMC emulations              | 29 |

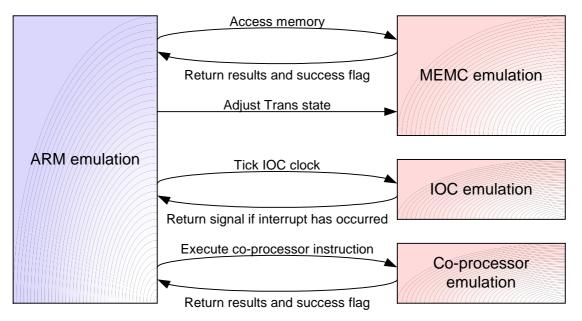

| Figure 13 – The interface between ARM and system emulation                                 | 30 |

| Figure 14 - The ARM interpreter loop                                                       | 31 |

| Figure 15 - Direct Translation of individual instructions                                  | 35 |

| Figure 16 – The recompilation steps using an intermediate code                             | 36 |

| Figure 17 - Recompilation without an intermediate representation                           | 37 |

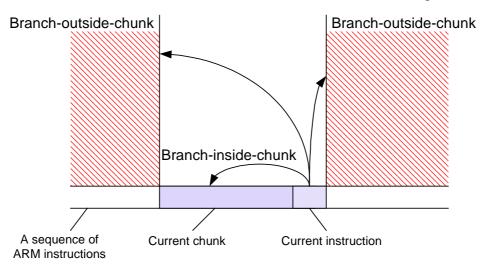

| Figure 18 - Deciding whether a branch is inside or outside the current chunk               | 44 |

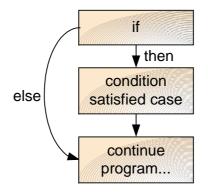

| Figure 19 - The control flow of an ifthen statement, showing forward branching             | 45 |

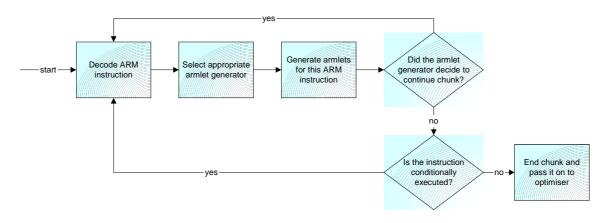

| Figure 20 - Outline of the decision process concerning whether to end the current chunk    | 47 |

| Figure 21 - The ARM processor modes and their register banks.                              | 48 |

| Figure 22 - The three stages of dynamic recompilation                                      | 53 |

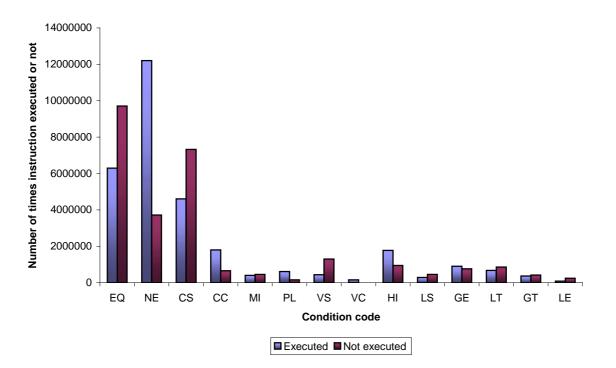

| Figure 23 – Observed execution statistics for conditionally executed instructions.         | 55 |

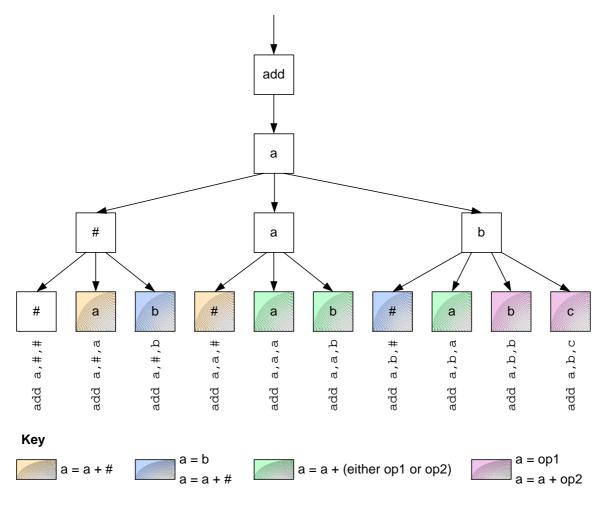

| Figure 24 - Permutations of the add armlet and appropriate x86 instructions                | 60 |

| Figure 25 - Decision tree for x86 instruction selection                                    | 61 |

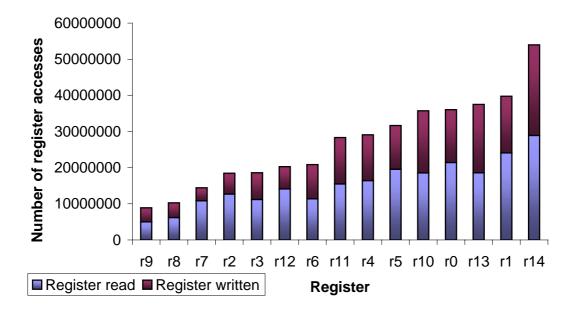

| Figure 26 - Register usage in RISC OS                                                      | 62 |

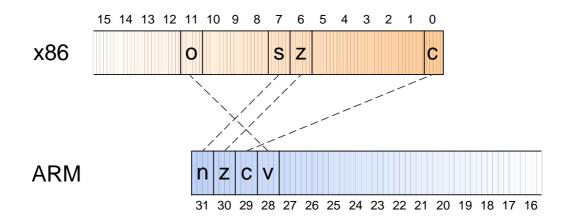

| Figure 27 - The ARM and x86 flag similarities                                              | 65 |

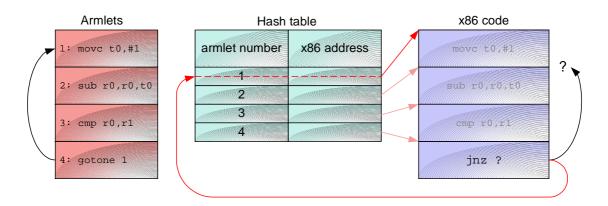

| Figure 28 - Identifying the x86 address of a given armlet to avoid backpatching            | 66 |

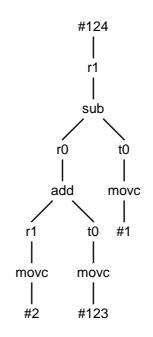

| Figure 29 - The relationship between armlets in constant evaluation                        | 68 |

| Figure 30 - The RISC OS initialising screen                                                | 71 |

| Figure 31 - Screenshot of the !Draw program, written in C, that comes with RISC OS         | 71 |

| Figure 32- Screenshot showing the RISC OS task manager and about box                       | 72 |

| Figure 33 - Screenshot showing the command line running ARM BASIC, written in ARM assembly | 72 |

## 1. Introduction

## 1.1. What is emulation?

Emulation allows software written for one computer system to be run on another. It does this by simulating the low level behaviour of the emulated hardware. The software's instructions are then followed and the emulator updates its state in the same was as the original machine would have done to its own registers and memory. As a result, the software can be made to run on another system identically to the way it would run on the system it was written for, despite the fact that the two may have different underlying hardware.

## 1.2. Applications of emulation

Emulation is an incredibly useful technique that has many different applications to problems across the field of computer science and the computing industry. These applications range from issues concerning the oldest computers to the very latest technologies. The following sections discuss some of these applications.

#### 1.2.1. Backwards Compatibility

Backwards compatibility with older systems (especially when application source code is no longer available) is often only possible through emulation. In business, emulation allows old hardware to be replaced without losing the use of the software that ran on it. In this way, emulation provides a cheap alternative to rewriting software from scratch for the new hardware.

In consumer computer systems, providing emulators for previous models has proved a successful way of migrating a customer base to the new generation of computers. For example, Acorn were able to lure customers to their 32 bit models by providing an emulator of their established BBC Micro range. Additionally Acorn was able to convert customers from other platforms by providing an emulator of an IBM-compatible PC.

#### 1.2.2. Portability

Emulation techniques can provide the capability of creating software that can run on any computer system without alteration. This is done by implementing an emulation of an abstract processor or 'virtual machine' (i.e. one that does not already exist) on various platforms. Compilers that convert programs into code for that virtual machine are then developed so that any program created using them can run on any of the systems that have an implementation of the virtual machine.

This concept is at least partially credited for the success for the Pascal language with the introduction of P-code in the late 1970s [1]. More recently, virtual machines have become prominent with the growth of the inherently multi-platform Internet. This has caused great interest in Sun Microsystems' Java language which compiles to a bytecode that runs on a Java Virtual Machine (JVM).

#### 1.2.3. Software Development

For some platforms, developing and testing software on the system itself is not always feasible. This might be because the hardware is still being developed, or in the case of embedded or portable systems, it may be expensive or time-consuming to install the software for testing. In conjunction with cross-platform development tools, emulators are commonly used to bridge the gap so that software can be developed quickly and cheaply before being implemented on the real hardware for final testing. Emulators such as SPIM [2], which emulates a MIPS processor, can provide a test environment for software that has features not available on the actual machine, for example with real breakpoints [3].

#### 1.2.4. Hardware Development

As the complexity of microprocessors has grown, emulation of new processors has often been used during the design phase. In the development of the ARM processor, emulations of the design were used from an early stage to verify the processor's logic.

In some processors, emulation is built into the hardware for backwards compatibility, for example the 16 bit 65816 processor (used in the Super Nintendo game console) can emulate in hardware the 8 bit 6502 processor (used in the older Nintendo Entertainment System) [4]. Other processors, such as the Crusoe range produced by Transmeta, have made emulation a central part of their design. By using dynamic binary translation techniques at a low level inside the processor, Crusoe processors are able to emulate an x86 processor at a comparable speed to the real thing but using less power [5].

#### 1.2.5. Historical preservation

Figure 1- Screenshot of the Manchester Baby emulator, the original was built in 1948

Building replica machines of the first computers from the early 1940s is a time consuming and costly business. In order to preserve the 'feel' of the first computers, historians have developed emulators of these early machines, such as Martin Campbell-Kelly's Warwick EDSAC Simulator [6] and my own Manchester Baby Simulator [7], shown in Figure 1. Since the original machines have often been destroyed over the years, these emulators continue to provide cheap and widespread access to them.

In recent years, the first home computers of the early 1980s have been superseded by systems more than powerful enough to emulate them. Sentimental attachment to the older computers has motivated many programmers to develop emulators for them on their modern home computers. This has gathered momentum resulting in a wealth of emulators covering almost every consumer computer ever made. Increasingly the emulator authors are striving to emulate the latest technology, resulting in the situation where systems that are still being sold commercially are already available under emulation for free.

## 1.3. Processor emulation techniques

#### 1.3.1. Importance of CPU emulation

The emulation of the central processing unit (CPU) is one of the core parts of any emulator in the same way the real CPU is one of the core parts of any computer. To emulate a processor running at 8 MHz, assuming a conservative average of 2 cycles per instruction (which is fair for an ARM2 processor) requires the emulator to emulate around 4 million instructions per second. From this it is clear that the CPU emulation can consume a large fraction of the processing time in any emulator, and therefore that the CPU emulation is extremely important for the emulator's overall performance.

There are several types of CPU emulator: the type chosen depends on the requirements placed on the emulator. The terminology and general concepts of these classifications are derived from concepts in compiler design, with the emulated machine's code being treated as the source language to the interpreter or compiler.

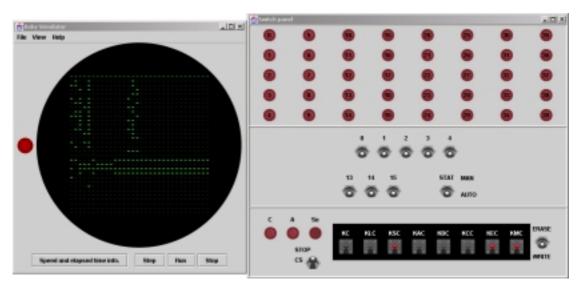

#### 1.3.2. Interpreter

Interpreting emulators work in much the same way as the emulated processor's fetchdecode-execute loop, shown in Figure 2. The emulated environment is first initialised to a known start state, which tends to involve setting the emulated registers, memory and interrupt timers to their initial values (as they would be on the real machine). The emulator then proceeds fetching the next instruction from emulated memory. The fetched instruction is then decoded in order to select the emulator's corresponding subroutine. The selected subroutine is then called which updates the emulated environment's registers and memory in the same way as that instruction's execution would have updated the machine's registers and memory. The whole process then repeats.

This method has several advantages:

- It is relatively simple to design and implement.

- It has relatively low memory requirements, since there is no data stored other than the emulated environment.

- There are no problems handling self-modifying code.

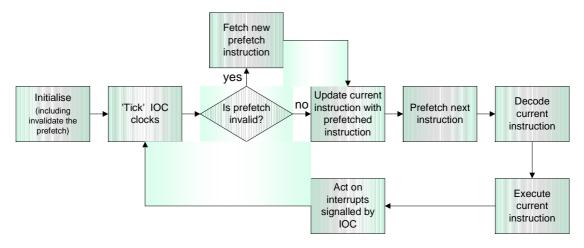

Figure 2 - The Fetch-Decode-Execute loop of a processor or interpreting emulator

Because of these advantages, particularly the simplicity, most emulators are implemented using this method. In emulators for embedded and portable devices, memory constraints can make interpreting the only feasible solution (for example the Java Virtual Machine for the Psion Series 5mx [8]). However, the interpreting method suffers the significant disadvantage of being the slowest approach.

The reason for this is that interpreting emulation is a fairly naïve algorithm that ignores the principle of locality (as utilised in processor caches) [9]. This is an empirical observation that an "[emulated] program spends 90% of its time in 10% of its code". There are three aspects to this principle:

| Temporal locality –   | once an instruction is executed it is likely to be executed |

|-----------------------|-------------------------------------------------------------|

|                       | again soon.                                                 |

| Spatial locality –    | the next instruction is likely to be near the current       |

|                       | instruction.                                                |

| Sequential locality – | the next instruction is likely to be immediately after the  |

|                       | current instruction.                                        |

An interpreting emulator only takes into account the current instruction being emulated. It is unable to utilise any previous times the instruction may have been emulated or the instructions emulated before and after it. As a result, the same sequence of instructions in a loop has be fetched and decoded unnecessarily by the emulator many thousands of times. The problem is summarised by the philosopher George Santayana's comment that, "those who cannot remember the past are condemned to repeat it" [10]. Fortunately other more complex emulation methods exist that are able to take advantage of the principle of locality.

#### 1.3.3. Dynamic Recompiler

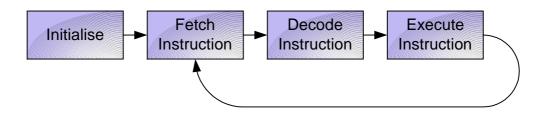

Dynamic recompilation is one method that attempts to avoid the shortcomings of interpreting emulators. Rather than only looking at the current instruction being executed, dynamic recompilers act on chunks of sequentially emulated instructions. The idea is that by storing information about that chunk the first time it is emulated, using this information will make all of its subsequent emulations faster. This is the same idea used by processor caches in transferring executed code to a faster storage area to benefit subsequent executions.

A dynamic recompiler identifies a section of code to be emulated and checks to see if it has been emulated before. If it has not then the dynamic recompiler generates a chunk of native machine code (i.e. machine code for the computer that the emulator is running on). This code updates the emulated environment as if those instructions had been emulated. Every successive time that this section of code needs to be emulated, the native machine code chunk is executed again, removing the need for repeated fetching and decoding of emulated instructions. By repeatedly identifying sections of code and executing machine code for them as shown in Figure 3, the emulated environment's state is updated correctly.

Figure 3 - The dynamic recompilation decision process

Dynamic recompilers have the advantage that they are significantly faster than interpreting emulators. However, they can have large memory overheads as a result of storing many chunks of native code for long periods of time, making them unsuitable for some embedded applications.

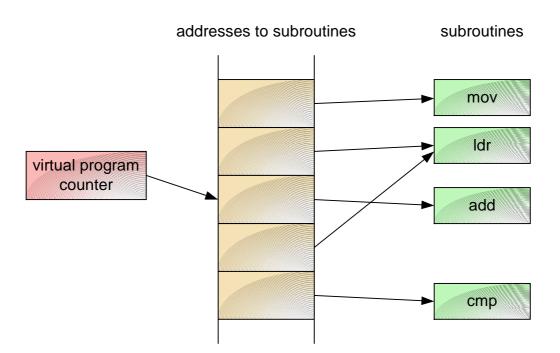

#### 1.3.4. Threaded Code

Threaded code [11] works in a similar way to dynamic recompilation. However, rather than generating native machine code, a list of addresses of handwritten subroutines is generated, that performs the emulation for each instruction. The list is stepped through one by one and each subroutine called to emulate the instructions, as shown in Figure 4. Since each handwritten subroutine is fixed during development, they are not as flexible and therefore not as fast as code generated by a dynamic recompiler. However, threaded interpreters do have the advantage that they are easier to implement and can be completely portable to a new platform with no modification as they need not use any machine code [12]. For languages such as Java that execute on a virtual machine which does not lend itself to having its code dynamically generated in this way (because of security requirements), threaded code is a good alternative to an interpreter to improve the performance of an emulator.

Both dynamic recompilers and threaded code can incur problems as a result of caching the information they generate. If the program code at an address in emulated memory changes, whether because a new program is loaded, the memory map changes, or the program is self-modifying, the previously generated code that is

associated with that address will be incorrect. How often this occurs on the emulated system can affect the benefits gained from caching this information.

Figure 4- The execution of threaded code

#### 1.3.5. Static Recompiler

Rather than recompiling code at run time (during emulation) as is done in a dynamic recompiler, static recompilers generate all the code before hand in the same way as a traditional programming language compiler. This has the benefit that that there is no time-consuming recompilation process when the emulation is running, making the emulation faster. The generated code can also be more optimal than that generated by a dynamic recompiler since better optimisation techniques can be applied that are too time-consuming to use dynamically.

Translating machine code before run-time can have complex problems. An inability to differentiate program code from data is one such problem. This is complicated by calculations that manipulate the value of the program counter. For example, the following section of ARM code shows a jump table that might be compiled from a C switch statement. This code could set the pc to a very large range of values depending on the value of r0 which is difficult to determine at compile time.

| add | pc,pc,r0,lsl #2 | ; | pc = pc + (r0 * 4)      |

|-----|-----------------|---|-------------------------|

| mov | r0,r0           | ; | nop for pipeline effect |

| b   | case0           | ; | go to case0 if r0 is 0  |

| b   | casel           | ; | go to casel if r0 is 1  |

| b   | case2           | ; | go to case2 if r0 is 2  |

|     | •               |   |                         |

|     | •               |   |                         |

|     | •               |   |                         |

|     |                 |   |                         |

Static recompilers alone cannot cope with code modification at run time as they have no way of updating the code that they execute. The only way that they can support this is to additionally implement one of the other three emulation methods to fall back on. As a result, static recompilers are not particularly suited to emulating an entire computer system, where code is frequently changed by loading new programs.

Static recompilation is better suited to the field of binary translation where attempting to convert a single executable program from one platform to another as such code modification is not normally an issue. Multi-platform operating systems such as Windows NT, Solaris and various flavours of Unix, then provide the environment that the program is executed in, rather than fully emulating a computer system as with normal emulation [13].

#### 1.3.6. Summary

In summarising this review of the different CPU emulation techniques it is important to emphasise that dynamic recompilation techniques allow the fastest execution of emulated instructions, without the limitations of static recompilation.

### 1.4. This Project

#### 1.4.1. Motivations

Most of the hundreds of emulators developed in the past few years emulate systems that are outdated and from the previous generation of computing to the systems being used to emulate them. As a result, the power of the host system dwarfs that of the one being emulated and performance is not a problem.

However, any emulator that attempts to model a more recent system has a significant challenge, as the complexity of modern processors is an order of magnitude greater than earlier systems. As well as being more complex, these emulated processors have clock speeds that are a reasonable proportion of the host system's processor clock speed. In order to emulate such modern systems at a reasonable speed, difficult approaches to emulation such as dynamic recompilation have to be employed.

Several dynamic recompilers have been developed in recent years to meet such demands. Unfortunately almost all have significant limitations. Commercial emulators such as VirtualPC [14], Ardi's Executor [15] and Apple's DR emulator [16], while impressive, tend to limit the information released to brief overviews in white papers (for commercial reasons). Many of the ground-breaking, freely available emulators such as UltraHLE [17], Corn [18] and PSEmu Pro [19] remain closed source and little information is released about their techniques. Other free emulators, that are open source, tend to lack documentation and use primitive techniques (such as direct translation and pre-assembled templates, see section 5.2). Additionally many of these emulators are for video game consoles that do not suffer the same complexities as emulators for computer systems (such as a full operating system, and an ability to load multiple programs).

Developments in Java Virtual Machine technology have been a good source of information on dynamic recompiling methods. However, due to the nature of stack-

based java bytecode relative to register-based machine code, many significant problems have been ignored (such as condition flags, interrupts and exceptions). Academic research on the subject tends towards the problems of binary translation [20], erring towards the complexities of static recompilation and retargetablity and away from emulating a full computer system.

As a result of these limitations there is a significant omission in the computing literature concerning emulating real computer systems using dynamic recompilation, something I hope to rectify with this report.

#### 1.4.2. Aim

The aim of this project is to emulate as accurately as possible a modern microprocessor, the ARM, using dynamic recompilation techniques.

#### 1.4.3. Previous work

There are several ARM emulators already in existence that have been developed for various purposes:-

| ARMulator    | ARM Ltd's own very accurate emulator of most models<br>of ARM processor, designed to be flexible enough to<br>debug developing software or alternatively completely<br>model every aspect of the inner workings of the<br>processor. [21] |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ArcEm        | The first Acorn Archimedes emulator. This makes use<br>of a modified version of the ARMulator for the ARM<br>emulation. [22]                                                                                                              |

| ARM2         | Only able to run simple programs in BBC BASIC as an alternative to the Unix shell. [23]                                                                                                                                                   |

| Archie       | The first Acorn Archimedes emulator for MS DOS. [24]                                                                                                                                                                                      |

| SWARM        | Used to model the internal ARM data path to facilitate research into possible modifications. [25]                                                                                                                                         |

| Red Squirrel | The first Acorn Archimedes emulator for Windows.[26]                                                                                                                                                                                      |

| ARMphetamine | A dynamically recompiling emulator for a subset of the ARM processor. Unfortunately support for exceptions, interrupts and processor modes was omitted. [27]                                                                              |

| Sleeve       | User mode emulator for use with Riscose [28], an implementation of the RISC OS API for Linux. Unfortunately it does not support exceptions or other processor modes. [29]                                                                 |

| Leeds Model | An executable formal specification of an A                       | .RM6  |

|-------------|------------------------------------------------------------------|-------|

|             | processor written in SML for use in a for verification. [30, 31] | ormal |

|             | Vermeation. [50, 51]                                             |       |

Unfortunately, many of these existing emulators such as ARMulator, SWARM and the Leeds Model are used for purposes other than emulating a real machine. Others such as ARM2, ARMphetamine and Sleeve are designed to only run a limited amount of application-level code and are not suitable for emulating a complete machine. The remaining three, ArcEm, Archie and RedSquirrel all emulate an ARM processor, though suffer from the inherent speed problems associated with interpreted emulation.

#### 1.4.4. Approach

The accuracy of a CPU emulator is extremely hard to measure. This can be done empirically by compatibility (what software can run), or quantitatively by completeness (how much of the processor's facilities it emulates). Different levels of completeness might include support for:

- small stand-alone programs in a test environment.

- interrupts

- exceptions

- processor modes

- coprocessors

To develop the dynamic recompiler to support as many of these as possible, it is helpful to emulate all the other hardware (MMU, graphics etc.) required by a system. This allows scope for using real applications and operating systems to be emulated as tests of accuracy.

Given the anticipated time scale and the size of the problem of implementing a dynamic recompiler, efforts had to be taken to reduce the workload. Rather than attempt to implement the dynamic recompiler as well as the emulation of the rest of the hardware, the approach taken is to make use of an existing (interpreting) emulator for a complete system. By removing the CPU emulation implemented by a third party and adding the dynamic recompilation in its place, the remainder of the system emulation can be utilised as required without distracting from the development of the recompiler.

## 2. Analysis

### 2.1. Introduction to the ARM

#### 2.1.1. Background

The ARM processor was the first commercial 32 bit RISC processor. It was developed at Acorn (ARM originally standing for Acorn RISC Machine), in the mid-1980s in an effort to develop a processor for use in their new range of computers to succeed the 8 bit 6502-based BBC Micro.

The majority of Acorn's processor research team in collaboration with Apple were later spun-off as a separate company, ARM (Advanced RISC Machines) Ltd. Today the ARM design is licensed to over 50 semiconductor companies who manufacture the processors, including many of the largest names in computer hardware, as shown in Figure 5 [32].

Figure 5 - ARM's semiconductor partners who manufacture the processors

As a result of the low price and low power consumption of the ARM, it has been widely adopted for embedded systems and portable devices such as mobile phones. It has also been used in a wide range of consumer computers from desktop machines such as Acorn's RISC OS series (for which it was originally designed) to home consoles such as the 3DO and the Sega Saturn console (where the ARM is used for sound processing), as well as arcade machines such as the Sega NAOMI system. The ARM has really become known for use in portable devices such as the Apple Newton, the Psion Series 5 and Nintendo's Gameboy Advance handheld games console, shown in Figure 6. With over 400 million ARM-based systems being produced in the year 2000, up from 182 million the previous year, the rate of growth of ARM products has been phenomenal.

Figure 6 - The Nintendo Gameboy Advance, one of many portable ARM-based devices.

#### 2.1.2. Technical introduction

Parts of the ARM design were based on the concepts of the Berkeley RISC chip [33], developed by postgraduates at the University of California at Berkeley in the early 1980s. The ARM adopted some of the RISC concepts, such as a load-store architecture (memory access is only possible through explicit load and store instructions), fixed length instructions (all instructions are encoded in 32 bits) and 3-address instructions (i.e. a destination and two operands). Other RISC-specific concepts, such as delayed branches and every instruction executing in a single cycle, were rejected. The designers at Acorn were forced to keep the architecture very simple as they had insufficient processor design experience to attempt anything more complex [34]. As a result, Steve Furber, one of the lead designers of the ARM, noted that it is, "less radical than many subsequent RISC designs" [35].

The ARM has 15 general-purpose registers; the 16<sup>th</sup> being dedicated to the PC, fewer than for many RISC processors (most having at least 32) but significantly more than most CISC processors. In true RISC style, only simple operations can be performed in an ARM instruction, leading to the divide operation and other more complex operations being omitted. The instruction set is extremely orthogonal to the extent that even the PC can be used as the operand or destination of most instructions.

One of the major strengths of the ARM design is its flexible attitude to condition flags. Every single ARM instruction is conditionally executed depending on the status of the condition flags. In other processors, conditional execution is only available on branch instructions (i.e. to jump to a subroutine if a condition is satisfied). After the influence of the RISC concept, conditional execution has often been extended to move (on x86) and test instructions (on MIPS) to reduce the number of conditional branches needed. The caveat to this flexibility on the ARM is that additionally all instructions have to be able to adjust or not the condition flags.

The other major strength is the ability to perform logical, arithmetic and rotational shifts on instruction operands, while still only taking up a single clock cycle. This combined with the 3-address structure allows incredible flexibility in a logic or arithmetic instruction. Additionally the ARM has extremely flexible block memory access instructions. These allow any combination of the 16 registers to be stored to or loaded from memory in a single instruction. Although not comprehensive (i.e. unable

to even perform a divide), the flexibility of individual ARM instructions makes them extremely powerful.

The uninitiated reader is directed to Appendix A for an overview of the ARM assembly language. This is useful both to get a feel for the subject of this project and as a brief tutorial to ARM instructions, knowledge of which is necessary for understanding the examples in this report.

### 2.2. Identifying the problem

#### 2.2.1. Other source processors considered

In the very early stages of planning, the ARM was not the only processor considered as the subject for the dynamic recompiler.

Many of the open-source hobby emulators available are for systems that use early 8 bit processors such as the MOS 6502 and Zilog Z80. These would be relatively simple candidates to implement and running at clock speeds of less than 4 MHz are able to be emulated at many times their real speed using interpreting emulation, making a dynamic recompiler interesting but unnecessary. Motorola's 16 bit 68000 processor was also a candidate, though because of an existing project to create a dynamic recompiler for it (as well as being competently emulated using interpreting methods [36]) it too was rejected.

Emulating a 32-bit Intel x86 processor around the level of an 80386 was briefly considered but rejected because the myriad of different instructions and idiosyncrasies could make it incredibly difficult to implement accurately. Additionally, despite the x86 being so pervasive in home computing, having its origins in the earliest processors of the 1970s means that it is not a typical modern architecture. Any successful emulation while commercially valuable would be of limited use for emulating other architectures.

The MIPS (Microprocessor without Interlocking Pipeline Spurs) processor, another 32 bit RISC architecture developed around the same time as the ARM, was a strong candidate. With MIPS processors having been used in both the Sony Playstation and Nintendo Ultra 64 games consoles, there are several open source emulators available for both platforms (some of which implement a crude form of dynamic recompilation) that could have been used. The MIPS is a more radical RISC design than that of the ARM, doing away with condition flags completely (instead conditional branches test register values [37]), which would simplify the implementation of a dynamic recompiler. The MIPS design goes to extraordinary lengths to optimise use of pipelining, with delayed branches and "bizarre" [38] effects such as multiply and divide operating outside the main pipeline. As a result, techniques developed for a MIPS dynamic recompiler would be unique to that project and might have less relevance to dynamic recompilers for other architectures.

The ARM was settled on for various reasons. The apparent simplicity of individual instructions and limited number of different operations meant that there are few complications (such as floating point or division) on top of the dynamic recompilation issues, or so it seemed initially. Other factors in the ARM's favour were the

availability of well-structured source code to emulators for Acorn RISC OS ARMbased machines and the difficulties of emulating an ARM processor at real world speed, a strong motivating factor. Additionally the relatively un-radical design of the ARM means that a dynamic recompiler for it still has relevance to dynamic recompilers for many other architectures both old and new, RISC and CISC.

#### 2.2.2. Which ARM architecture?

As a reflection of the multitude of different applications of the ARM processor, there are many configurations of ARM core currently marketed by ARM Ltd. and still more that are outdated. The question of which one to focus on for this project was carefully considered.

The original Acorn design for the ARM processor stored the PSR (Processor Status Register) in r15 along with the PC, only allowing space for a 26-bit-PC, as shown in Figure 7. After ARM was spun off as a separate company, their later designs separated the PSR and PC, allowing a full 32-bit-PC giving increased address space (4 Gb as opposed to 64 Mb). Most of these new processors retained the ability to execute 26-bit-PC ARM code for backwards compatibility, almost solely to support Acorn's RISC OS operating system which was written largely in 26-bit-ARM assembly.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 | 37 | 6 | 5 | 4 | 3 | 2 | 1  | 0   |

|----|----|----|----|----|----|-----------------------------------------------------|----|---|---|---|---|---|----|-----|

| n  | z  | с  | v  | i  | f  | program counter                                     |    |   |   |   |   |   | mo | ode |

|    |    |    |    | Γ  |    |                                                     |    |   |   | ٦ |   |   |    |     |

|    |    |    |    |    |    | n - negative flag                                   |    |   |   |   |   |   |    |     |

|    |    |    |    |    |    | z - zero flag                                       |    |   |   |   |   |   |    |     |

|    |    |    |    |    |    | c - carry flag                                      |    |   |   |   |   |   |    |     |

|    |    |    |    |    |    | <ul> <li>v - overflow flag</li> </ul>               |    |   |   |   |   |   |    |     |

|    |    |    |    |    |    | - interrupt disable flag                            |    |   |   |   |   |   |    |     |

|    |    |    |    |    |    | - fast interrupt disable flag                       |    |   |   |   |   |   |    |     |

|    |    |    |    |    |    | mode - processor mode                               |    |   |   |   |   |   |    |     |

|    |    |    |    |    |    |                                                     |    |   |   |   |   |   |    |     |

Figure 7 - R15 in 26-bit-PC ARM processors, containing both the PC and PSR

Other later additions to the ARM design have included the Thumb instruction set (a 16 bit encoding of a subset of the ARM instruction set), a 5-stage rather than 3-stage pipeline, 64 bit-result multiplication and Java bytecode execution [39]. These later additions do not have particularly wide ranging consequences for the core of the ARM emulation and could all be added to an ARM dynamic recompiler relatively easily later on.

It was decided that supporting both 32-bit-PC and 26-bit-PC modes in the initial development would be too much effort with no benefit for the recompilation techniques. Choosing 32-bit-PC emulation would be easier since the complexities of the combined PC and PSR would not arise. Additionally it would be similar to all recent ARM developments. In contrast choosing 26-bit-PC emulation would be harder, would not be as relevant to recent ARM developments but had the significant

advantage that it could be used to run RISC OS, allowing use of the large library of RISC OS programs for testing. 26-bit-PC mode was chosen for the available software and the challenge of the combined PC and PSR, with the issues of the 32-bit-PC mode being seen as a subset of those of the 26-bit-PC mode.

The architecture decided upon was the ARM architecture version 2a as implemented by the ARM3 processor. This was the final ARM processor without 32-bit-PC support, as used in the Acorn A5000 computer. The functionality of this architecture is a subset of that in architecture versions 3 and 4 (ARM6xx, ARM7xx, ARM8xx and StrongARM processors) for backwards compatibility [40].

#### 2.2.3. System emulator

Red Squirrel was chosen as the emulator the dynamic recompiler was to use for development and access was granted to the source code. Red Squirrel was favoured as it was still under active development by the author, the source was well structured with clearly separate CPU emulation and it is built using a good interactive development environment (Visual C++). It is important to remember that although Red Squirrel has been used during development, the dynamic recompiler is designed to have a clean generic interface so that it can be used with any emulator for an ARM-based system.

#### 2.2.4. Target processor

The principal target processor chosen was the 32-bit Intel x86 processor, as used in modern IBM-compatible PCs. This was selected largely because Red Squirrel was available for the platform. Additionally the x86's gargantuan CISC instruction set is practically the antithesis of the ARM's clean RISC design. As a result, converting from ARM to x86 (RISC to CISC) provides a challenging problem.

### 2.3. Getting started

#### 2.3.1. Preparation

Before approaching a problem of this scale, considerable time was spent researching methods used in other emulators and relevant technologies. Many different emulators and dynamic recompilers for various platforms were investigated. Work in similar fields such as JVM technology, binary translation and optimising compilers was also found to be relevant although sometimes not practical. Additionally a lot of learning about the ARM and x86 architectures was necessary, studying every detail from various reference manuals.

#### 2.3.2. Design overview

The dynamic recompiler is only a part of this project. In attempting to accurately convert fragments of arbitrary programs from one machine code to another, thousands of times a second, there is significant groundwork to prepare. There are two main parts to this work, an ARM disassembler necessary for debugging the rest of the development and an interpreting ARM emulator. This interpreter was to prove invaluable for investigating the problem, debugging and for making design decisions that could not be made any other way, it also forms a fundamental part of the complete system.

The early stages of the Fusion method for object-oriented design were employed to identify the relationships between various parts of the system. Unfortunately, this high level approach was inappropriate to be continued into the intricate details of the emulation that make up the majority of the project.

#### 2.3.3. Implementation

The implementation details of the project were restricted, based on the choice of Red Squirrel as the system emulator to be used. The Microsoft Visual C++ development environment was used to develop the dynamic recompiler. C++ was deemed a suitable language because of its low level features such as shifting and structure unions, its speed relative to many other higher-level languages and its object-oriented nature promoting good program structure. C++ was also the obvious choice given that it is the language used to implement Red Squirrel. As already mentioned Red Squirrel had been implemented for Windows and I saw no need to change that, though the project implementation has been kept as platform-independent as possible.

#### 2.3.4. Title

The final decision to be made in preparation was that of a title for the project. In attempting to follow in a long line of bad puns for ARM projects, initially there was little inspiration. As the project progressed an apt working title sprang to mind and has stuck: 'Tarmac' – it's very hard.

### 2.4. The System Design

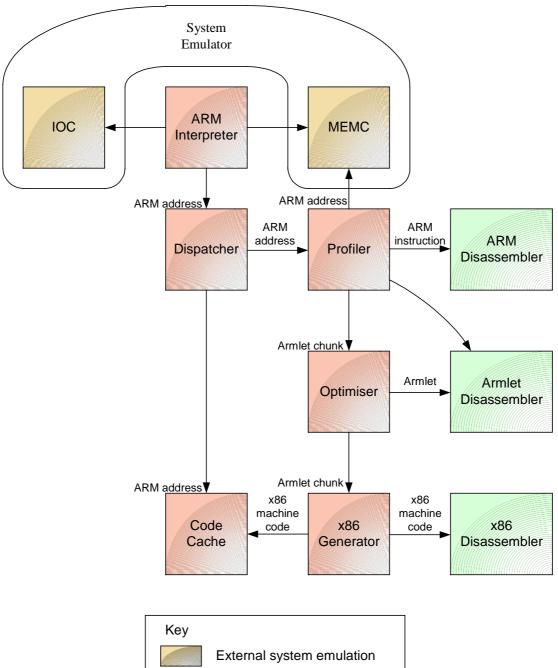

The overall system design comprises of several independent systems, as shown on Figure 8. The system object model is introduced at this stage to provide an explanation as to how the different components of the system fit together; however, the operation of the complete system is complex and will only be understood once the individual components have been explained.

The ARM interpreter communicates with the emulation of IOC and MEMC in order to drive the computer's emulation. The dispatcher is able to invoke the interpreter, the profiler or native code as required. When the profiler is invoked, it reads from memory the relevant ARM instructions and generates a chunk of intermediate code. The chunk of intermediate code is then passed on to the optimiser and finally to the x86 generator which creates x86 machine code. The machine code is then stored in the code cache so that the dispatcher can invoke it. The ARM disassembler, Armlet disassembler and x86 disassembler are all debugging tools that interact closely with the system during development.

Figure 8 - System Object Model

## 3. Disassembler

## 3.1. Purpose

Although not contributing to the emulation, the ARM disassembler developed in the early stages was an essential tool used in creating the dynamic recompiler. Throughout the debugging of the rest of the project, various sequences of ARM instructions had to be examined in order to determine where the program was going wrong. Using an existing disassembler that takes a binary file and outputs the disassembled code in a text file was of no use since the facility for disassembled code to be displayed with other information from the emulator was needed. Creating an ARM disassembler specifically for the project was also a chance to investigate the problems of decoding ARM instructions before attempting the interpreter.

## 3.2. ARM decoding

Figure 9 - ARM instruction set encoding

In emulators for older processors it is feasible to have a single look up table with the necessary number of entries (256 or 65536) to directly call a function to handle every

possible instruction encoding [42]. For a 32 bit processor like the ARM, with over 4 billion encodings possible this is no longer possible so a more complex decision algorithm for decoding is needed. Fortunately, with relatively few operations on the ARM, much of the 32 bit instruction encoding is taken up encoding operand registers or immediate values (which limits the permutations of different instructions).

The ARM instruction set, as shown in Figure 9, divides neatly into 11 different classes, largely distinguishable by the values in bits 24 to 27 of the instruction. It is on these bits that the disassembler performs initial decoding with further decisions being made as necessary specific to each case for the various other fields.

## 3.3. Design

As an example, take the case of a single data transfer instruction, such as:

When executed this takes the address from r2, logically shifts it left by 2 (effectively multiplying by 4), and that result added to r1 gives the address of the word to be loaded from memory into r0. The calculated address is then written back into r1.

As already stated, the single data transfer class of instruction is identified by performing a 'look up' on bits 24-27 of the instruction. Parts of that range of bits, such as bit 25, denotes that the modifier to r1 is a register rather than an immediate value and bit 24 denotes pre-index i.e. that r2 lsl #2 should be added to r1 *before* the memory access. As a result these two variations are decoded for free by virtue of being included in the look up table on bits 24-27, hence 4 variations of single data transfer disassembly for pre/post index and immediate/register are implemented.

Additional decoding then has to be used on bits 20,21,22 and 23 to decide whether the instruction is load or store, writeback or not, byte or word, increment or decrement respectively. The remainder of the instruction space is used to encode the registers involved, with r0 and r1 being encoded in bits 12-15 and 16-19 respectively. The logical shift left is denoted by bits 5 and 6, the use of r2 by bits 0-3 with the amount to shift by (i.e. 2) encoded in bits 7-11. Each of these separate sections affects the final string of text output by the disassembler.

While apologies must be made for the rather dry explanation, the length of the description highlights the critical problem with emulating an ARM processor - the complexity of decoding. Performing this kind of decoding in a debugging tool such as the disassembler is not a problem, however attempting to perform this millions of times a second in an interpreting emulator is.

#### 3.3.1. Testing

Being certain that the disassembler was accurate was of great importance, as bugs left undetected at this stage could compound the difficulty of debugging the rest of the project. In order to guard against this, large samples of disassembled text produced by disassembling real RISC OS programs, were systematically compared to the results from StrongEd [43]. StrongEd is a disassembler on the RISC OS platform and has been thoroughly tested during use by hundreds of programmers, this makes it a good source for comparison to the disassembler in order to verify it.

The use of the disassembler was so successful that the envisaged debugging graphical user interface (mentioned in the progress report) was unnecessary. In a previous emulation project [44], a debugging interface to execute single instructions one at a time was implemented; however, in this case, having a flexible disassembler proved sufficient. The disassembler was invaluable for testing all other parts of the project but particularly the interpreting emulator.

## 4. Interpreter

## 4.1. Purpose

The purpose of the ARM interpreter is to emulate any instructions that are not dynamically recompiled. It is also needed to provide a fully working model of the ARM processor to aid in the development of the dynamic recompiler.

## 4.2. The problem with JIT

In attempts to speed up Java Virtual Machines, *just-in-time* (JIT) compilers have often been employed. In a JIT JVM when a Java method is called for the first time it is recompiled into native code and stored to be used every subsequent time the method is called [45]. As a result of always executing recompiled code, a JIT JVM need have no interpreting emulator.

The JIT JVM gets most of its performance boost from the second (and subsequent) times that a method is called, as the first time it is called, expensive recompilation has to take place. Indeed recompiling and executing a method once can take longer than simply interpreting it and as a result, overall speed is only improved if a method is called multiple times. The converse observation of the principle of locality is that an '[emulated] program executes 90% of its code only 10% of the time'. Having to recompile this 90% of code that is only rarely reused can lead to an undesirable performance reduction in the JIT JVM.

This problem is particularly true of program initialisation where most of the code executed will only be executed once while the program loads. Interpreting these sections of code can often give better performance than recompiling them. The lesson is that there is no point in recompiling code that is never going to be executed again.

## 4.3. The HotSpot<sup>™</sup> alternative

Rather than recompile every method when it is called, Sun Microsystems' HotSpot<sup>TM</sup> JVM is more sophisticated and only recompiles selected methods. The first few times a piece of code is executed, the Java bytecode is interpreted and some analysis is done on the code to identify performance 'hot spots'. Performance 'hot spots' are sections of code that take a lot of processing time and would benefit from optimisation by recompiling to native code [46]. It is only these sections of code that are actually recompiled since other areas that are not executed enough to recoup the cost of recompilation, would slow the emulation. This demonstrates the necessity of an interpreting emulator as a critical part of a dynamic recompiler and is the approach taken in this project.

To avoid confusion the reader should note that JIT is sometimes used to refer to any JVM which recompiles Java bytecode. In this report, the naming convention used by Sun Microsystems has been followed where a JIT JVM is one that recompiles every piece of code that is emulated (and therefore does not require an interpreting emulator).

#### 4.4. Quantifying the JIT problem

The difference between the JIT, HotSpot and interpreting emulators is best demonstrated in some quantifiable way. This can be done by calculating the relative total cost of emulating a chunk of code for each algorithm, using the following formulae.

Interpreter  $n c_i$ JIT  $c_{\rm r} + n c_{\rm c}$ Hotspot-style recompiler *if* n > t *then*  $t c_{\rm i} + c_{\rm r} + (n - t)c_{\rm c}$ else  $n c_i$

Where:

| $c_{i}$     | <ul> <li>– cost of a single interpreting emulation of the code.</li> </ul> |

|-------------|----------------------------------------------------------------------------|

| Cr          | <ul> <li>– cost of recompiling the code.</li> </ul>                        |

| $c_{\rm c}$ | <ul> <li>– cost of calling the recompiled code.</li> </ul>                 |

| n           | – number of times the code is to be emulated.                              |

| t           | – number of times the code is interpreted before being recompiled.         |

Dividing these results by n, gives the 'average cost per emulation', i.e. the average amount of processor time used to emulate a chunk of code just once. By assigning typical costs to these values in the ratio 1:5:25 for  $c_c:c_i:c_r$  with t as 1 (i.e. the hotspot-style algorithm interprets just once before recompiling) and varying the values of *n* used, the graph generated is as shown in Figure 10.

Figure 10 - The relative average cost per emulation of different emulation methods

From the graph it is clear that the JIT method is the cheapest approach for code that is executed many times (by a small margin). Unfortunately, this is coupled with an intolerable cost for code that is executed only once. Interpreting emulation, as expected, has the same cost for each emulation no matter how many times emulated. The hotspot-style algorithm has the best of both methods, combining a progressively cheaper emulation for high values of n relative to interpreting, with a large cost saving over JIT for the smallest values of n. It is this property that makes it the best approach to emulation.

## 4.5. Faster decoding

Since the interpreter affects the overall performance of the emulation, great pains have been taken to make the interpreter as fast as possible. The problem of decoding ARM instructions quickly, forced the design of the interpreter to take a more aggressive approach than the disassembler. Rather than decoding on the obvious instruction bits of 24-27, which would lead to an extensive (and expensive) decoding tree, decoding is performed on the byte from bits 20-27.

This leads to a 256-entry-table of the code to deal with all instructions and far more extensive specialisation (and therefore less decisions) for each entry. As a result, where in the disassembler a single entry covered the entire class of data processing instructions (logic and arithmetic operations), the interpreter table has 4 table entries just for variations of the add instruction that use immediate or register values and do or do not adjust the condition flags. The form of the resulting structure is shown in Figure 11.

```

switch( getField(currentInstruction, 20, 27) )

{

...

// add rd, rn, rm

case 0x08:

...

// addS rd, rn, rm

case 0x09:

...

// add rd, rn, imm

case 0x28:

...

// addS rd, rn, imm

case 0x29:

...

}

```

Figure 11 - The format of the interpreter's instruction decode table showing add instructions

This has the clear advantage of algorithmic efficiency by combining many decisions across the different classes of instruction into one fast look up. The disadvantage is that since there are large pieces of intricate code that may be identical or very similar, the complexity of the program increases dramatically leaving it more vulnerable than most to programmer error. To combat this, extensive templates are used throughout for common operations such as for getting the operands for data processing instructions.

## 4.6. Interfaces

The ARM emulation cannot emulate a complete system on its own. In Red Squirrel it is linked to an emulation of the IOC (Input/Output Controller) which manages interrupts, and MEMC (Memory Controller) which is an interface between the ARM and the system memory. Both the IOC and MEMC chips were custom designed by Acorn Computers Ltd. for their RISC OS machines but almost all ARM-based systems have some equivalent interrupt controller and memory management unit. The functionality provided by these subsystems is so closely linked to the CPU that in some ARM processors (such as the ARM7500) they are actually on the same chip [47].

As a matter of good design and in order that the results of the project could be used with any ARM system emulator, great care was taken to ensure that no dependency on Red Squirrel was established unnecessarily. As a result, the interface between the interrupt and memory controllers is through an extra indirect interface used throughout the ARM interpreter. The ARM emulation accesses memory through this interface indicating a logical address. This is passed to the MEMC emulation, which accesses the appropriate page in memory and updates any memory-mapped systems without the ARM emulation knowing any details about MEMC, as shown in Figure 12. The only other ARM to MMU action is where the ARM can set the 'trans' flag. The 'trans' flag is used for certain memory access instructions and forces the MMU to treat the memory access as if from a non-privileged mode irrespective of the current processor mode.

Figure 12 - Example of the interface used to separate ARM and MEMC emulations

Interrupts are likewise implemented transparently to the ARM emulation, with the ARM emulation signalling the IOC emulation at the start of each instruction's execution and IOC returning information as to whether an interrupt has occurred. This leaves the CPU emulation unburdened with the complexities of calculations and timings for the IOC emulation, having just to handle the effects of an interrupt that the software expects. This divorcing of the emulation of external systems is a strength as the finished project can then be used for a completely different machine's ARM emulation.

The third interface between the ARM emulation and the system emulation is that of coprocessors. From the earliest designs, the ARM has included a generic coprocessor

interface; used for floating point, signal processing and system control. While many types of coprocessor are relatively under-utilised on the ARM, the system control coprocessor is commonly included 'on-chip' for adjustments to the MMU and cache, and is emulated by Red Squirrel. The ARM interpreter uses Red Squirrel's emulation for the system control coprocessor, though the interface is generic enough and limited in its impact on the interpreter to be adjusted for any other ARM system emulator or coprocessor type.

The complete interface between the system emulation (at present, Red Squirrel) and the ARM emulation is summarised by the actions shown in Figure 13.

Figure 13 – The interface between the ARM and system emulation

The good design and minimal scope of these interfaces keeps the ARM emulation sufficiently distant from that of the rest of the system even for something like memory access which affects large parts of the ARM interpreter.

Further interfaces to remove the way in which the emulated state is stored from the way in which it is implemented were used internally to the ARM emulation. This is often frowned upon in emulators, where the extra layer of indirection in function calls is costly (when executed millions of times a second). However, it is necessary so that the way emulated registers and flags are stored can be adjusted for the dynamic recompiler without repercussions for the interpreter.

## 4.7. The emulation loop

As a result of pipelining, the looping used to emulate an ARM processor is slightly more complex than the simple fetch-decode-execute design described in section 1.3.2. In a real ARM processor, one instruction is being executed, the one after it is being decoded and the one after that is being fetched from memory at any one time. A 5-stage pipeline was implemented after the ARM7, adding buffer and write-back stages, though this does not affect this project [48].

As a consequence of the pipeline, the PC is always 2 or 3 instructions ahead of the current instruction being executed, depending on the circumstances. This means that in the rare event that an instruction changes the next instruction, the original version will already have been prefetched and will be executed unchanged (some games software is known to actually do this [49]). The solution is to emulate the prefetch by always fetching the next instruction in the iteration of the loop before it is to be executed. On a branch or adjustment of the PC, the pipeline is flushed and the prefetched instruction invalidated causing the prefetched instruction to have to be reloaded.

As described in the previous section, interrupts are triggered by 'ticking' the IOC clocks. The prefetched instruction value is then decoded and emulated and after the instruction is executed, any interrupts signalled by the IOC emulation are dealt with. The loop then returns to tick the IOC again, as shown in Figure 14.

Figure 14 - The ARM interpreter loop

#### 4.8. Implementation

In any software, using assembly language allows faster programs to be produced than using a high level language. This is even more so in emulation where similarities between the way the emulated and emulating processors adjust condition flags can be utilised in a way not possible in higher level languages. However, due to the scale of the problem of writing an ARM interpreter (over 5000 lines of C++), as well as the interface to Red Squirrel being entirely in C++, it was not suitable to implement the interpreter in assembly. Additionally, despite selecting the x86 architecture as the target for the dynamic recompiler, the project is not necessarily tied to that platform so a multi-platform language such as C++ is desirable.

During the development it became apparent that algorithmic considerations are not the only factors affecting program performance. In order to escape the overheads of extra function calls in implementing interfaces as described previously, it is important to leverage the optimisation facilities of the implementation language. For example, in C++ the use of the inline directive can significantly improve performance by inlining methods [50].

## 4.9. Debugging

Bugs in the ARM interpreter are extremely difficult to identify. The main problem is that the effects of a slight anomaly in the emulation, such as incorrectly setting a single bit on a single iteration of a loop, may not become apparent until millions of emulated instructions later. This problem was appreciated well in advance and precautions were taken in comparing descriptions from several sources at every stage of the implementation.

It is not feasible to exhaustively test every possible ARM instruction looking for problems. However, many of the earliest bugs identified were found by writing small test programs on an Acorn Risc PC, to test subsets of the instruction set. These programs are then loaded into a 'dummy' memory and emulated until a mov pc,r14 instruction is reached (normally used to end a program). The results visible in the emulated registers are then compared to the results from the real hardware to find errors.

Following the success of using test programs, a line by line inspection was made of the code, searching for problems, at each stage verifying operation with the manuals. Often the manuals are vague, conflicting or simply omit boundary cases leaving only experimentation with the real hardware and Red Squirrel's existing interpreting emulator. For example, one source declares that for the mul instruction, "r15 [the PC] may be used as one or more of the operands" [51], while another states that doing so has, "unpredictable results" [52].

Other sources and emulators highlighted features of the ARM's operation that were not at all obvious [53, 54]. A good example of this is where the instruction

movs r0,#256

will clear the Carry flag for no obvious reason whereas in most cases the movs instruction only adjusts the Negative and Zero flags. Investigations showed that because of the way the immediate value 256 is encoded in the instruction, as 1 rotated right by 24 places, the value of the last bit to be rotated across the end of the register is 0 and the Carry flag is therefore set to 0.

Having attempted to accurately translate every aspect of the ARM processor from the manuals to a fully working model and tested it thoroughly, the final test was to attempt to boot Acorn's operating system, RISC OS. This is seen as an extremely intensive test of the compatibility and completeness of the emulator as the operating system performs a lengthy system test on start up and will refuse to boot at the slightest error.

A copy of RISC OS v3.11 was extracted from an Acorn A5000 where it is stored on ROM and set up to be loaded into Red Squirrel's emulated memory map. The loading code and dummy memory previously used for test programs were deactivated and the interfaces adjusted to access Red Squirrel's IOC and MEMC emulation. Despite all the testing that had gone before, a different approach was required to get the ARM interpreter to a fully working state before moving on to the dynamic recompiler.

Miniscule errors either in the interpretation of the sources, or in the sources themselves initially prevented the ARM interpreter from running RISC OS. To locate these errors, a certain number of instructions (typically 50,000 at a time) were emulated on Red Squirrel's interpreter, dumping the disassembled instruction and all register and flag values to a text file after every instruction. Performing the same test on my ARM interpreter and then running file comparisons on the two dumps was a good way to find the smallest discrepancy between the two interpreters.

Even with such a mechanical bug detection system, the linear search for differences was still a slow one. It was found that in the event of a single bug, the execution of every successive instruction was affected. As a result a manual binary search could be performed across the execution space at intervals of several hundred thousand instruction emulations in order to find discrepancies. Once discrepancies were found, time-consuming investigation into the cause of the problem ensued, an example of such an investigation follows.

The  $6,531,120^{\text{th}}$  instruction executed in loading RISC OS is tegp pc,#3. The instruction executed immediately after it is at a completely different address in memory (0x1C) and is b 0x381134C. The only difference between the two emulations is that after the first instruction, r14 in Red Squirrel's interpreter had been incremented by 4 to 0x3811757, while r14 in my interpreter had been set to 0.

The teqp instruction performs an exclusive-or on the two operands, in this case the PC and the value 3, updating the PSR with the result. As shown in Figure 7, this adjusts the processor mode flags, changing to supervisor mode. Immediately after that instruction an IRQ (Interrupt Request) exception occurred, deducible from the PC changing to  $0 \times 1C$  (the IRQ vector  $0 \times 18$  incremented by 4 because of pipelining effects).

When an IRQ exception occurs, the ARM processor changes the register bank used for r13 and r14, copies the PC from r15 into r14 and jumps to the IRQ vector. From examining the emulation of the IRQ exception, it was found that incorrectly r14 was being updated with the value of r15 *before* the register bank changed, instead of afterwards (and therefore r14\_irq was unmodified and held the value 0).

While a complete understanding of the investigation may escape the reader, an appreciation of the difficulty of discovering the cause of the problem should not. Many such problems had to be tracked down, which took considerable time. Although most parts of Red Squirrel are deterministic, unfortunately the keyboard interrupts are asynchronous resulting in non-deterministic behaviour. This manifests itself by the ability to run the interpreter on the same test data twice and get different results, making automatic comparisons between the Red Squirrel interpreter and my own impossible. Fortunately, this did not affect RISC OS until the later stages of loading and slower manual examination of test dumps allowed sufficient testing.

### 4.10. Compatibility

The level of compatibility achieved by the ARM interpreter is extremely good. RISC OS boots completely to the desktop and is able to run high-level software, including

the very complex ARM BASIC interpreter. This is quite an achievement and allowed development of the dynamic recompiler to continue with confidence, having a working model of the complete ARM processor for comparison.

## 5. Recompilation

### 5.1. Overview

The recompilation system has a simple purpose: to generate native x86 machine code to emulate a given sequence of ARM instructions. This generation must be done quickly so that it does not slow down the emulation but should also make the generated machine code as fast as possible.

An algorithm programmed for two different architectures could be implemented optimally for each processor. However, despite the algorithm being identical, the resulting machine code would have little in common. Ideally a dynamically recompiling emulator would be able to reverse engineer the machine code to the original algorithm and then optimally recompile it for the target processor. Unfortunately automatically inferring the high level semantics of an arbitrary piece of machine code is a difficult problem. Under the limited processing conditions of a dynamic recompiler, attempting to do so is simply not feasible.

The alternative is to emulate the ARM instructions in the same way as the ARM interpreter does. This means generating native machine code that adjusts the registers and flags of the emulated ARM processor, in the same way as executing the instructions would on the real machine. In this way, we avoid the problems of trying to deduce the high level operation of a program.

## 5.2. Methods of generating native code

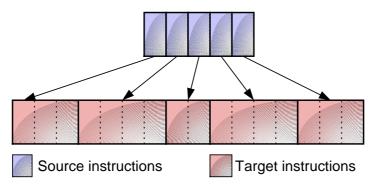

Direct Translation is the simplest approach of generating native machine code, where instructions are translated one by one. Once a source instruction has been identified, a predefined section of native code is generated for that instruction. The next instruction is then decoded and translated and appended to the machine code generated for the first. All this method does is to take pre-assembled 'covers' of target machine code and put them in the same order as their corresponding source instructions, as shown in Figure 15. This method removes the cost of fetching and decoding emulated instructions relative to an interpreting emulator though does little else. Although relatively straightforward to implement, this method is inflexible as it is unable to take account of instructions either side of the current one being translated and is therefore fairly crude in its optimisations.

Figure 15 - Direct Translation of individual instructions

Better forms of recompilation are performed on entire sequences of source instructions at once. In this way, optimisations over several instructions can be used to generate much faster code than is possible using direct translation.

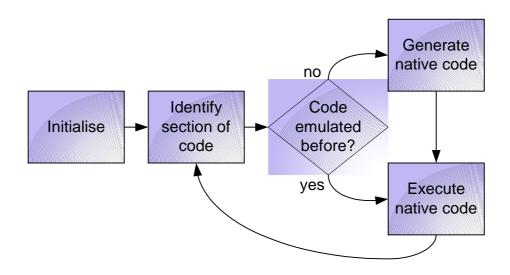

## 5.3. The use of intermediate code

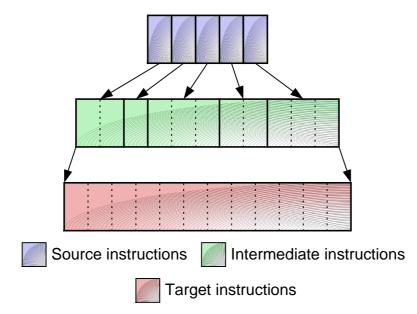

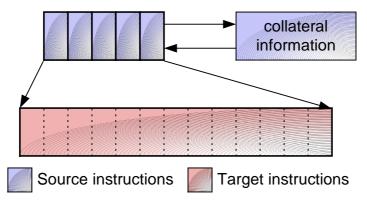

There are two main ways to perform optimising dynamic recompilation: with or without an intermediate code. An intermediate code is a third representation (other than source and target machine codes) of the instructions to be translated. The source code is converted into intermediate code and then the intermediate code translated into the target machine code, as shown in Figure 16. This method has been used in recompiling JVM's [55] and other dynamic recompilers [56].

Figure 16 – Recompilation using an intermediate code

Advantages:

- The native code generator can be changed to 'retarget' the dynamic recompiler so that it translates from ARM to a different target platform, without affecting the rest of the system.

- Recompiling ARM instructions that have many stages (such as Block Data Transfer) is complex and benefits from being decomposed to smaller simpler intermediate instructions.

- It is easier to debug than going direct from ARM to x86 as the intermediate code maps more closely to x86 than complex RISC instructions.